kaiyun体育官方网站 登录入口 正如Ayar Labs所说-kaiyun体育官方网站 登录入口

来源:华尔街见闻

这家名为Ayar Labs的光芯片初创公司,接力于突破畴昔的数据传输模式,谋略是将光通讯平直置于封装上,而不是受到IO密度问题、数据速率扩展和电子封装到封装互连的功率低效性限度。

频年来,跟着AI竞争愈演愈烈,岂论是传统照旧新兴的处理器巨头齐在围绕CPU、GPU和AI加快器伸开了强烈竞争。尤其是AMD、Intel和英伟达三大标记性巨头,由于三者的竞争包含其后者的追逐逆袭、新市集的来势汹汹、老巨头的不甘东谈主后等情节,使得这三个巨头的任何动向尤为蔼然。这三家公司围绕着东谈主工智能和PC伸开明争暗斗亦然无人不晓。

但近日,这三家公司漠视联手,投资了一家名为Ayar Labs的光芯片初创公司。

三大芯片巨头,看上光互连

Ayar Labs今天晓喻,已获取由 Advent Global Opportunities 和 Light Street Capital 领投的 1.55 亿好意思元融资,旨在垄断其光学 I/O 工夫突破 AI 数据迁移瓶颈。这使该公司的总融资额达到 3.7 亿好意思元,并将公司估值升迁至 10 亿好意思元以上。

正如Ayar Labs所说,本轮融资的范畴和投资者的教导标记着 Ayar Labs 的又一个重要里程碑,该公司正在准备其光学措置决策,以策略性地配合客户道路图进行多数目坐褥。该公司暗示,参与本轮融资的有名公司就涵括了刻下最炙手可热的芯片三大巨头AMD Ventures、Intel Capital 和 NVIDIA ,其他新策略和金融投资者包括 3M Ventures 和 Autopilot。值得一提的是,在之前,Ayar Labs也拿了包括Applied Ventures LLC、Axial Partners、Boardman Bay Capital Management、GlobalFoundries、IAG Capital Partners、Lockheed Martin Ventures、Playground Global 和 VentureTech Alliance在内的广漠有名企业和机构的钱。

Ayar Labs 首席实施官兼连合创始东谈主 Mark Wade 暗示:“跳跃的 GPU 提供商 AMD 和 NVIDIA 以及半导体代工场 GlobalFoundries、Intel Foundry 和 TSMC,再加上 Advent、Light Street 和咱们其他投资者的援救,突显了咱们的光学 I/O 工夫再行界说 AI 基础设施将来的后劲。”“咱们相配红运,在这轮融资中,Light Street 在工夫特定投资方面的深厚专科常识以及 Advent 刚劲的私募和成长股权布景为咱们提供了援救。”

据关连贵府走漏,Ayar Labs成立于 2015 年,公司团队由来自英特尔、IBM、好意思光、Penguin、麻省理工学院、伯克利和斯坦福的许多顶尖工夫各人组成。

在官网的先容中,Ayar Labs将公司定位为光学互连措置决策规模的相易者,其提供的居品数据传输速率与 AI 格外。公司暗示,在刚毅到 AI 模子的复杂性和范畴正在以传统互连工夫无法处理的速率增长,他们开发了业界首个光学 I/O 措置决策,使客户梗概最大限制地升迁连接增长的 AI 基础设施的诡计恶果和性能,同期缩小老本、蔓延和功耗。Ayar Labs指出,公司的光学 I/O 措置决策基于盛开次序,并针对 AI 执行和推理进行了优化,领有刚劲的生态系统,使其梗概凯旋大范畴集成到 AI 系统中。

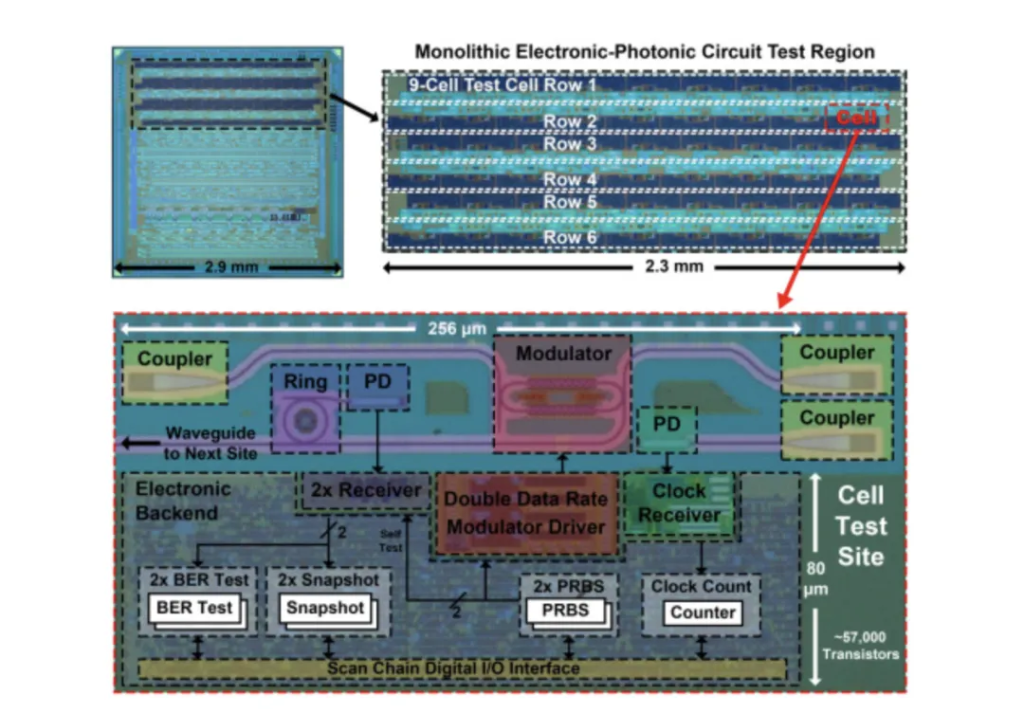

如上图所示,Ayar Labs 暗示,公司故事的发祥不错缅想到公司在2010年的发布的一篇名为《Open foundry platform for high-performance electronic-photonic integration》的论文。据先容,该著作证明汲取那时商用电子 45 nm SOI-CMOS 代工工艺制造的具有 3 dB/cm 波导损耗的光子器件。通过垄断现存的前端制造工艺,光子器件与电子器件单片集成在与晶体管不异的物理器件层中,完结 4 ps 逻辑级蔓延,而不会缩小晶体管性能。

在著作中,他们展示了一个 8 通谈光学微环谐振器滤波器组和光调制器,它们均由集成数字电路限度。通过开发一种不需要任何工艺基础设施更变的器件联想方法,不错完结鄙俚可用的高性能光子电子集成电路平台。

在著作的证明阶段他们强调,论争展示的电子-光子平台是一种可探问的、低老本的垄断现存电子代工场基础设施的方法,可用于制造高性能光子器件和开始进的 CMOS 晶体管。使用薄 SOI-CMOS 工艺无需进行代工场里面编削,只需进行简便的后处理即可完结精良的无源光子性能,排斥了之前责任中存在的波导损耗瓶颈。著作先容的滤波器组解复用器和调制器等开拓,以及面前正在开发的集成光电探伤器,组成了先进电子工艺中光子互连平台的基础,该工艺可用于制造现在的微处理器。该代工平台的通用性质使咱们不错使用开始进的工夫,这将极地面促进悉数 VLSI 和光子系统及应用规模的新式电光片上系统的研究。

恰是基于这个研究,Ayar Labs在2015年宣告成立,然后在次年获取了种子轮投资(GlobalFoundries 参与了种子轮融资)。

Ayar Labs,聚焦措置的问题

在具体先容Ayar Labs的居品之前,咱们先先容一下他们具体思措置什么问题。

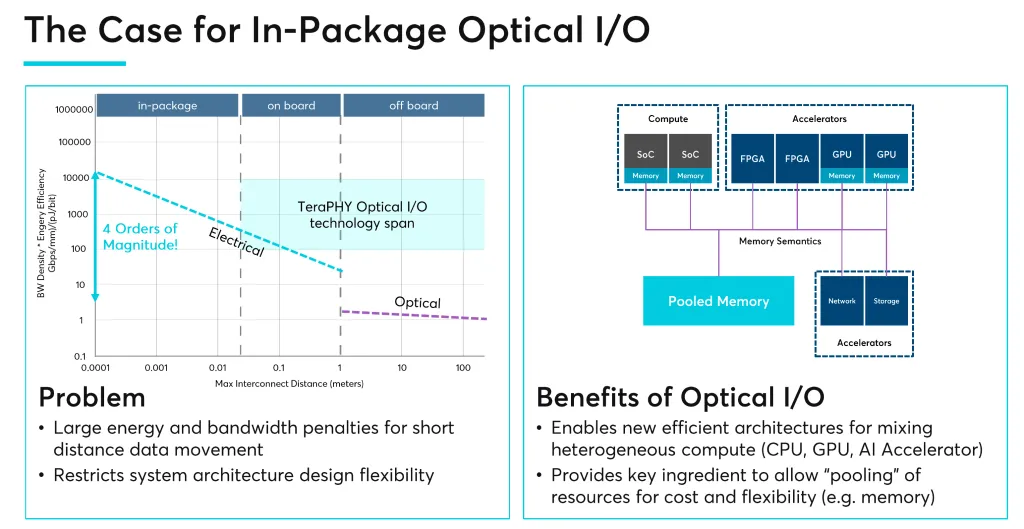

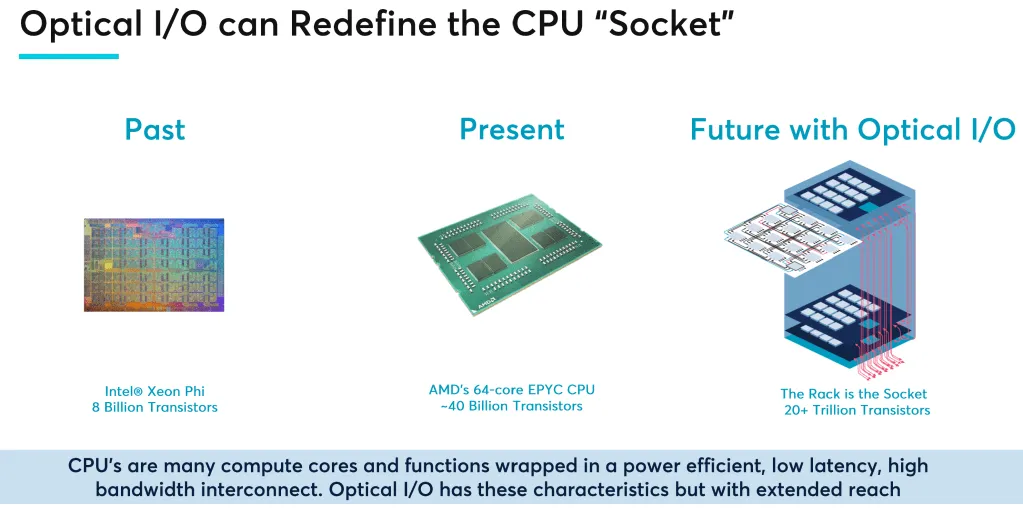

正如之前好多报谈中所说,高性能诡计引擎存在带宽和信号问题,这也曾不是什么奥妙了。要是你思要以合理的每秒容量快速地将数据输入和输出,从而让引擎中的数十到数万个中枢保持劳作,那么要是你要对峙使用铜线,就必须尽可能细腻地贯穿它们,岂论是插入堆叠内存的插入器上的走线,照旧收支 SerDes 的电线,以将诡计引擎贯穿在通盘以并走运行。

问题在于电线的长渡过长。每次将带宽增多一倍时,由于信号失真,您齐必须将电线长度减半。这是物理学和材料科学的问题,每个东谈主齐知谈最终铜线将被光纤取代。何况由于东谈主工智能责任负载对带宽的宏大需求,将来几年内这似乎将确切成为不可幸免的趋势。

Ayar Labs也恰是这么的“光”参与者,接力于突破畴昔的数据传输模式。

据了解,他们的谋略是将光通讯平直置于封装上,而不是受到 IO 密度问题、数据速率扩展和电子封装到封装互连的功率低效性限度。Ayar Labs 的主要不雅点是,在 1cm 到 10cm 的传输范围内,光学 IO 比刻下的电子系统更高效。措置数据传输功率推广问题的最好方法是,惟有您将数据传输到此距离之外,就切换到光学。

有名行业分析机构semianalysis暗示,转向共封装光学器件有许多刚正。举例数据不需要从处理器发送到网卡,也不需要通过立志的光收发器。处理器自己也不错从简多量老本,因为无须将太多的芯单方面积专用于大型高速电气 SerDes。

鉴于 Ayar Labs 已加入盛开的 UCIe 次序,Semianalysis以为他们的芯片将使用该左券看成与外部公司芯片接口的基础层。UCIe 援救英特尔、ASE 和台积电的许多封装选项。在处理器方面,英特尔、AMD、博通、好意思光、联发科和 GUC 齐是该定约的成员。UCIe 极地面缩小了将第三方芯片集成到封装中的参预门槛,这反过来应该会缩小 Ayar Labs 获取联想告成的参预门槛。此外,Ayar Labs 也明确援救高密度扇出、英特尔的 EMIB 和其他硅中介层工夫。

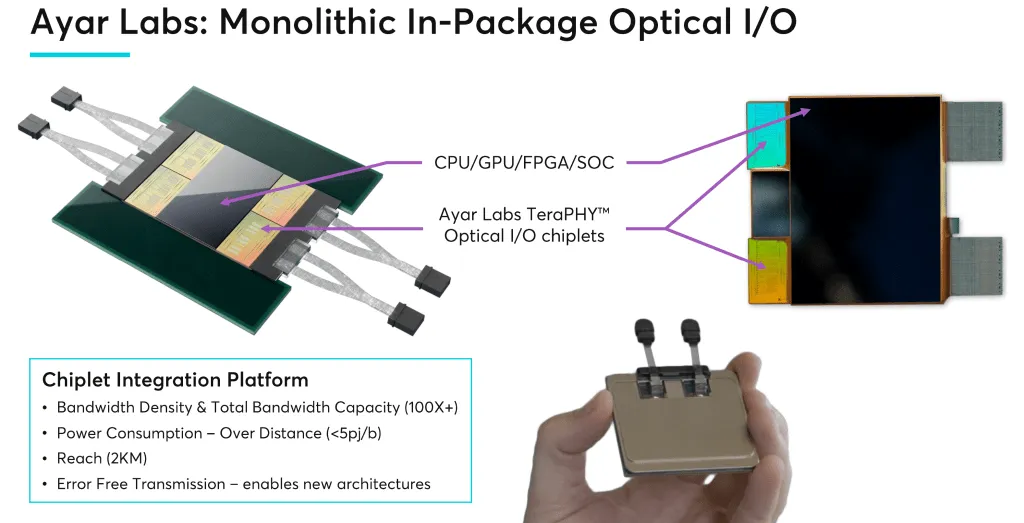

面前,Ayar Labs有两种主要的居品:一是SuperNova 光源——这是封装外部的辛苦光源,不错将其视为位于 ASIC 封装外部某处的光电源;另一个是TeraPHY 光学 I/O 芯片,这种硅片包含约 7000 万个晶体管和 10,000 多个光学器件。据先容,他们将硅光子器件集成到 CMOS 工艺中,制成咱们看成芯片出售的硅片。该芯片集成到客户 SOC 封装中。

从官网不错看到,SuperNova辛苦光源是 Ayar Labs 光学 I/O 措置决策的撑持,亦然业界首款合适 CW-WDM MSA 次序的 16 波长光源,可提供多达 16 种波长的光并为多达 16 个端供词电。与 Ayar Labs TeraPHY 光学 I/O 芯片组相引诱,与传统互连(可插拔光学器件 + 电气 SerDes)比拟,该措置决策可提供 5 至 10 倍的更高带宽、10 倍的更低蔓延和 4 至 8 倍的更高能效。光学 I/O 排斥了 I/O 瓶颈,特出了工艺限度,并为下一代 AI 架构开释了立异架构。

TeraPHY光学 I/O 芯片组则是一种体积小、功耗低、微辞量高的铜背板和可插拔光学通讯替代决策。TeraPHY 芯片组的模块化多端口联想可承载八个光通谈(格外于 x8 PCIe Gen5 链路)。这款业界创始的光学 I/O 芯片组将硅光子学与次序 CMOS 制造工艺相引诱。它适用于现存的系统级封装架构,不需要 SoC 定制。

按照该公司CEO Mark Wade所说,Ayar Labs面前的主要买卖模式是销售实质居品。他暗示,SOC规模也曾发生了悉数范式回荡,以股东 chiplet 的汲取。要是你掀开 ASIC 的盖子,你会看到里面有多个芯片。于是,Ayar Labs将所谓的“KGD”光学芯片装入客户的封装中销售。来到光学 I/O 芯片方面,Ayar Labs将其看成创收居品销售,客户只需平直从咱们这里购买芯片即可。

Wade强调,Ayar Labs的市集策略专注于措置光子学规模的多数目、高质料制造问题。咱们与 GlobalFoundries、Applied Materials、英特尔和台积电等主要公司树立了策略配合关系,并与扫数一线 CMOS 制造商伸开配合。

Ayar Labs还与大型 AI 系统规模的相易者 Nvidia 树立了策略配合股伴关系,共同将咱们的工夫融入将来的 AI 系统。公司的平直客户正在构建 SOC 和 SOC 系统,其一流生态系统包括 Nvidia、AMD、英特尔、博通和高通等公司。

“构建大范畴 AI 模子的末端客户(举例 Anthropic 和 OpenAI)至关重要。数据中心在尝试扩展 AI 责任负载时出现了许多严重问题。咱们发现,这些公司对将来的愿景与咱们多年来的预测相似,这确认了这少许。”Ayar Labs CEO Mark Wade强调。“咱们的告成取决于能否参预这些规模。咱们正在应酬光子工夫方面的挑战,至极是在多数目、高质料制造方面。这种方法使咱们梗概与行业主要参与者配合,同期高亢最终用户的需求,从而突破东谈主工智能工夫的界限。”Mark Wade接着说。

Ayar Labs 本年八月曾暗示,将发布其光学 I/O 工夫来取代芯片内的铜线。该公司正在开发将光学 I/O 放入芯片结构中的工夫,并已研究该工夫十多年。该工夫允许芯片里面完结更快的通讯,旨在取代速率较慢的铜线。

“借助光学 I/O,你不错突破几十米以致几百米的距离,然后贯穿更多的 GPU 或加快器,”Wade 说。

大范畴商用在即?

在东谈主们很容易以为,Nvidia、AMD 和英特尔的投资预示着这些公司正在寻求以某种风物在其诡计引擎中部署 TeraPHY 光学传输过头 SuperNova 激光源。咱们知谈,他们的早期投资者HPE早在 2022 年 2 月就与 Ayar Labs 达成了一项策略投资和配合左券,将硅光子学添加到其“Rosetta”Slingshot 互连中。

但在回复The Next Platform盘问时,Ayar Labs 买卖运营副总裁 Terry Thorn 开打趣说:“他们齐是投资者和公司,咱们正在与他们通盘探索许多道理的契机——其中大部分咱们面前还不成褒贬。”咱们不错思象这种情况会发生,但还有许多其他方法不错完结共封装光学器件,这三家公司也齐有发明我方居品的民俗。

换而言之,通过这些投资,这些芯片公司可能仅仅思更潜入了解 Ayar Labs 正在作念的事情。但正如Mark Wade在之前的采访中所说,在好多场景中会需要使用光贯穿。

如他所说,当Ayar Labs刚运行研究这个问题时,许多早期见地齐来自高性能诡计社区——你知谈,国度实验室正在建造的大型机器。这些大型系统最初发现它们存在多量数据迁移问题,这些问题运行成为悉数系统性能的瓶颈。这即是Ayar Labs称之为“煤矿中的金丝雀”的 2010 年至 2015 年的时刻段,那时的近况标明底层诡计工夫存在问题。

之后,跟着东谈主工智能责任经过运行出现,以及图像识别、推选引擎等早期责任负载——但其后,至极是当更动器模子上线并运行启用新的东谈主工智能应用步地时,咱们参预了生成式东谈主工智能期间。但枢纽是要刚毅到,组成这些东谈主工智能诡计系统主干的诡计系统看起来像高性能诡计架构。

“因此,十年前在高性能诡计中发生的不异数据迁移挑战现在运行出现在东谈主工智能系统中,并成为悉数系统性能的瓶颈。”Mark Wade强调。

Mark Wade指出,这是一个多方面的问题。您必须让东谈主们在功率受限的情况下将更多带宽传输到更长的距离。因此,这些系统的功率限度并不是无尽的。每个级别齐存在热和功率密度问题 - 芯片级、封装级、系统板级、机架级。因此,每个级别齐存在功率问题。蔓延是您必须更仔细查验的处所。

“如今,东谈主们使用铜线和电气 I/O 以电气风物传输高带宽的风物,您时常会作念一些事情,举例添加纠错,因为您要尝试收复在以电气风物传输数据时发生的扫数低恶果和数据损坏。在光学方面,您不错以一种优雅的风物措置这个问题,从而开脱纠错。因此,您不错获取更轻量级的纠错架构,但这会影响蔓延。”Mark Wade说。

为了完结上述谋略,Ayar Labs一直在丰富其居品线。

要是你看一下道路图,就会发现Ayar Labs每隔几年就会将每个芯片的带宽翻一番。他们的操办从 4 Tbps 增多到 8 Tbps,然后是 16Tbps 和 32 Tbps,这是每个芯片的带宽。Ayar Labs还下调了一些向量——每个芯片的带宽、每个封装实例化多个芯片的才智、扩大悉数封装级别带宽以及不错从封装中开释的带宽基数。Ayar Labs的客户频频蔼然咱们不错从他们的封装中开释些许带宽,以及在什么样的功率密度束缚下。至极是跟着东谈主工智能系统的发展,每个封装中更高的带宽开释变得越来越重要,同期也升迁了贯穿的基数。

面前,Ayar Labs的每个芯片有 8 个端口,每个芯片组有 8 个端口。假定每个封装有 4 个芯片组,则您的贯穿端口为 32 个,您不错将扫数这些端口贯穿到不同的处所。

预测将来,Wade暗示:“咱们面前在实验室中与客户共同开展的责任,实质上是为了在两到三年后完结初次大范畴市集部署。”

写在终末

其实光学并不是一项新工夫——光纤确切参预工夫规模是在 70 年代。咱们运行建造海底电缆和访佛的东西,最终贯穿互联网。光学工夫是无人不晓的。

然而将数据平直以光学风物从诡计包中移出的需务实质上是一个格外新的气象,这与电气 I/O 问题的恶化速率接洽。咱们的应用步地需要更高的带宽和更好的能效——这运行突破现存的基于电气 I/O 的系统。但挑战在于,你不成只把东谈主们使用的工夫和居品用于东谈主们可能练习的更次序化的措置决策,举例使用以太网的可插拔收发器。要是我在数据中心内迁移 100 Gbps、400 Gbps 或 800 Gbps,那么这些也曾是光学可插拔收发器了。问题是,要是你掀开这些收发器并检讨里面的东西,你会发现它们莫得平直扩展到诡计结构的特质。

因此,要完结上述谋略,除了要面临尺寸、元件数目、老本结构,以及扫数这些组件的拼装风物外。还有功率恶果、热聪惠度等问题,还有“我不成平直将收发器放入诡计机封装中”的一系列问题。

“因此,咱们必须从新运行发明一种具有正确底层特质的工夫:密度、开拓尺寸、动力恶果,更重要的是,梗概集成到制造工艺中,从而在 CMOS 范畴下运行。咱们必须掌持奈何将该工夫纳入封装,因为这是一种真梗直范畴的应用。扫数这些特质在每一步齐是挑战,咱们公司的一部分,以及咱们多年来所奋力的一部分,实质上是在一步步措置这些问题。”Mark Wade暗示。

面向这个市集和契机,除了Ayar Labs之外,Lightmatter、Celestial AI 、Eliyan以及国内的曦智和一大堆的处理器、晶圆厂和封装厂齐在奋力,为硅光子学成为诡计引擎和互连之间的桥梁各异常招。

著作来源:半导体行业不雅察,原文标题:《Nvidia、AMD和Intel漠视联手,投资一家光芯片公司》

风险领导及免责条件

市集有风险,投资需严慎。本文不组成个东谈主投资提议,也未磋议到个别用户特殊的投资谋略、财务景况或需要。用户应试虑本文中的任何意见、不雅点或论断是否合适其特定景况。据此投资,连累自诩。

海量资讯、精确解读,尽在新浪财经APP

海量资讯、精确解读,尽在新浪财经APP

连累剪辑:丁文武 kaiyun体育官方网站 登录入口